# Imperial College London

MENG INDIVIDUAL PROJECT

IMPERIAL COLLEGE LONDON

DEPARTMENT OF COMPUTING

## Better Than Registers: Designing an Instruction Set to Make O-o-O Microarchitecture Simpler and Faster

Author: Stacey Wu Supervisor: Prof. Paul Kelly

Second Marker: Dr. Holger Pirk

June 22, 2022

#### Abstract

In modern computer architecture, out-of-order superscalar processors use complex register rename logic to remove false data dependencies between instructions and improve instruction-level parallelism.

We design a novel architecture which encodes the data dependencies in the instruction at compile time and removes register renaming in the out-of-order pipeline. We design a new Instruction Set Architecture(ISA) and define the new instruction set in an ISA emulator. We also provide compilation, assembler and linker support to compile the program from C source code to executable file.

We modify the conventional out-of-order processor to remove register renaming and simulate the architecture with compiled C program in a cycle-accurate architecture modelling tool. Throughout the project, it is found that the performance benefits come from more efficient misprediction recovery mechanism.

We run some experiments and demonstrate that the run-time performance improves by up to 3.5% from removing register renaming from the reduced pipeline stages which reduces the branch misprediction penalty.

We also explore the microarchitectural benefits of the new architecture from removing register renaming and provide a qualitative analysis on other benefits arising from hardware simplification. This architecture also provides further performance benefits to exploit its statically constructed data dependence for selective recovery to furthuer reduce its mis-speculation penalty.

#### Acknowledgements

First and foremost, I would like to thank Prof. Paul Kelly for his continuous support and mentorship throughout the project, especially agreeing to schedule last minute meetings and replying emergency emails at random hours of the day.

My gratitude goes to Prof. Hidetsugu Irie and his research group from University of Tokyo for providing the source code of STRAIGHT backend.

I would also like to thank Ph.D. candidate Luke Panayi for helping me understand LLVM backend and providing me with numerous support in this project.

I am grateful for the amount of support and help I receive from my friends, Barbara, Gowoon, Tejas, Jason and many more throughout my project and degree. Without them, I would not have been here.

Last but not least, I would like to thank Tilman Roeder for the help in last minute running experiments, plotting diagrams and countless emotional support during the many breakdowns throughout the project.

## Contents

| 1 | Intr         | roduction 8                                                                                                                               |

|---|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1          | Objectives                                                                                                                                |

|   | 1.2          | Contributions                                                                                                                             |

|   | 1.3          | Conclusion                                                                                                                                |

|   | 1.4          | Report Structure    9                                                                                                                     |

| • | <b>D</b>     | 10                                                                                                                                        |

| 2 |              | kground 10                                                                                                                                |

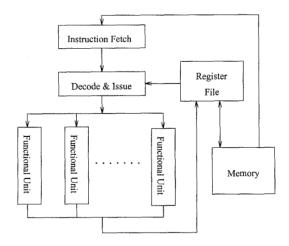

|   | 2.1          | Superscalar Architecture       10         2.1.1       Out-of-Order Execution       10                                                     |

|   |              |                                                                                                                                           |

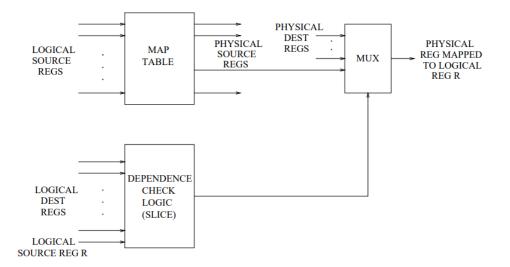

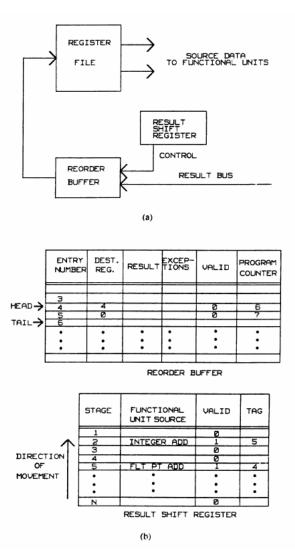

|   |              | 2.1.2       Register Renaming       11         2.1.2       Boundar Buffer       12                                                        |

|   |              | 2.1.3Reorder Buffer122.1.4Performance Bottleneck12                                                                                        |

|   | 9.9          |                                                                                                                                           |

|   | $2.2 \\ 2.3$ |                                                                                                                                           |

|   | 2.5          |                                                                                                                                           |

|   | 9.4          |                                                                                                                                           |

|   | 2.4          | gem5                                                                                                                                      |

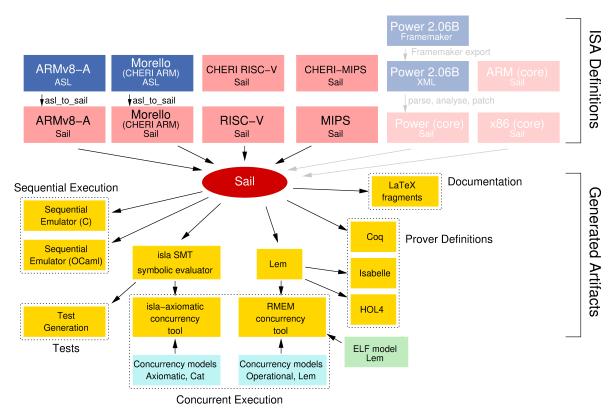

|   |              | 2.4.1 ISA                                                                                                                                 |

|   |              | 2.4.2 CPU Model                                                                                                                           |

|   | ~ -          | 2.4.3 Architecture Simulation                                                                                                             |

|   | 2.5          | Conclusion                                                                                                                                |

| 3 | Rel          | ated Work 17                                                                                                                              |

| Ŭ | 3.1          | Register Renaming                                                                                                                         |

|   |              | 3.1.1 Complexity of Rename Logic                                                                                                          |

|   |              | 3.1.2 Rename Logic Optimisation                                                                                                           |

|   | 3.2          | Misprediction Recovery                                                                                                                    |

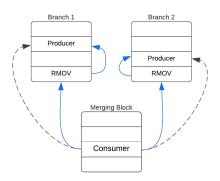

|   | 0.2          | 3.2.1 Selective Recovery                                                                                                                  |

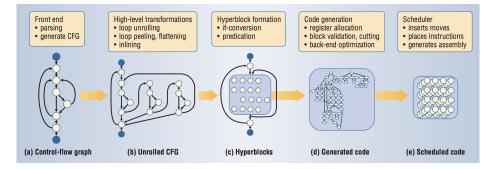

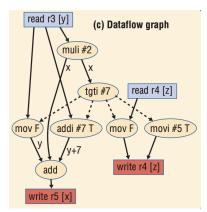

|   | 3.3          | EDGE Architecture                                                                                                                         |

|   | 0.0          | 3.3.1 Construction of DFG                                                                                                                 |

|   |              | 3.3.2 Register Rename Simplification                                                                                                      |

|   |              | 3.3.3 Selective Recovery                                                                                                                  |

|   | 3.4          | STRAIGHT Architecture                                                                                                                     |

|   | 0.4          | 3.4.1 Instruction Set Architecture (ISA)                                                                                                  |

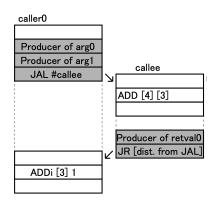

|   |              | 3.4.2 Compilation Flow Part 1 – Calling Convention                                                                                        |

|   |              | 3.4.2       Complication Flow Part 1 – Calling Convention       21         3.4.3       Compilation Flow Part 2 – Code Generation       21 |

|   |              | 3.4.4 Performance Evaluation                                                                                                              |

|   | 3.5          | Conclusion                                                                                                                                |

|   | 0.0          |                                                                                                                                           |

| 4 | Des          | ign 24                                                                                                                                    |

|   | 4.1          | Aim                                                                                                                                       |

|   | 4.2          | Instruction Set Design                                                                                                                    |

|   |              | 4.2.1 Major Differences From STRAIGHT Instruction Set                                                                                     |

|   |              | 4.2.2 Modification on RISCV ISA                                                                                                           |

|   |              | 4.2.3 Special Registers                                                                                                                   |

|   |              | 4.2.4 New Instructions                                                                                                                    |

|   | 4.3          | Compilation                                                                                                                               |

|   | 4.4          | Assembly                                                                                                                                  |

|   | 4.5                                                                | Architecture Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27                                                                                                                         |

|---|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|   |                                                                    | 4.5.1 Instruction Set Semantics Definition – Proof of Concept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27                                                                                                                         |

|   |                                                                    | 4.5.2 Single Cycle Processor – Accuracy Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27                                                                                                                         |

|   |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28                                                                                                                         |

|   | 4.6                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 29                                                                                                                         |

|   | 1.0                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

| 5 | Imr                                                                | ementation – ISA Definition and Compilation Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30                                                                                                                         |

|   | 5.1                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30                                                                                                                         |

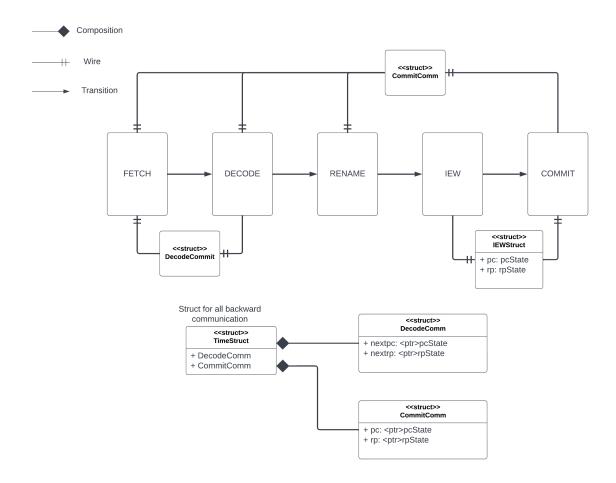

|   | 5.2                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33                                                                                                                         |

|   | 5.3                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33                                                                                                                         |

|   | 0.0                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33                                                                                                                         |

|   |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33                                                                                                                         |

|   |                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                            |

|   |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33                                                                                                                         |

|   | 5.4                                                                | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 34                                                                                                                         |

| 0 |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>.</b>                                                                                                                   |

| 6 |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35                                                                                                                         |

|   | 6.1                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35                                                                                                                         |

|   |                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35                                                                                                                         |

|   |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35                                                                                                                         |

|   |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35                                                                                                                         |

|   |                                                                    | 6.1.4 RP Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35                                                                                                                         |

|   | 6.2                                                                | Single Cycle Modelling – Accuracy Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35                                                                                                                         |

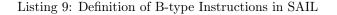

|   |                                                                    | 6.2.1 Simple CPU Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36                                                                                                                         |

|   |                                                                    | 6.2.2 Register Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36                                                                                                                         |

|   |                                                                    | 6.2.3 RP Increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 37                                                                                                                         |

|   |                                                                    | 6.2.4 Zero Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37                                                                                                                         |

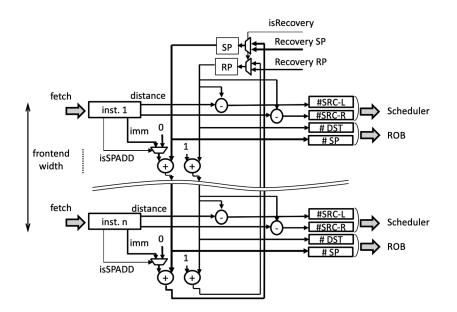

|   | 6.3                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37                                                                                                                         |

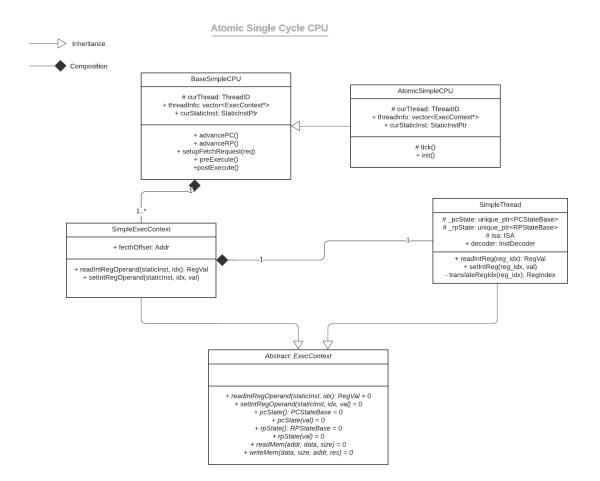

|   |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37                                                                                                                         |

|   |                                                                    | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38                                                                                                                         |

|   |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38                                                                                                                         |

|   |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

|   | 64                                                                 | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

|   | 6.4                                                                | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40                                                                                                                         |

| 7 |                                                                    | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                            |

| 7 | Eva                                                                | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 40                                                                                                                         |

| 7 |                                                                    | Conclusion       4         uation       4         Evaluation Hypothesis       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 40<br><b>41</b><br>41                                                                                                      |

| 7 | <b>Eva</b><br>7.1                                                  | Conclusion       4         uation       4         Evaluation Hypothesis       4         7.1.1       Theoretical Performance Improvement       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 40<br><b>41</b><br>41<br>41                                                                                                |

| 7 | <b>Eva</b><br>7.1<br>7.2                                           | Conclusion       4         uation       4         Evaluation Hypothesis       4         7.1.1       Theoretical Performance Improvement       4         Evaluation Methodology       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40<br>41<br>41<br>41<br>42                                                                                                 |

| 7 | <b>Eva</b><br>7.1                                                  | Conclusion       4         uation       4         Evaluation Hypothesis       4         7.1.1       Theoretical Performance Improvement       4         Evaluation Methodology       4         Verification of Correctness       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40<br>41<br>41<br>42<br>43                                                                                                 |

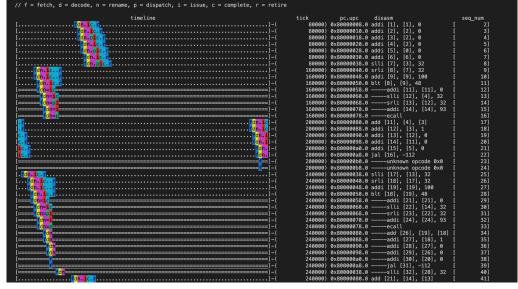

| 7 | <b>Eva</b><br>7.1<br>7.2                                           | Conclusion       4         uation       4         Evaluation Hypothesis       4         7.1.1       Theoretical Performance Improvement       4         Evaluation Methodology       4         Verification of Correctness       4         7.3.1       Sum of Arithmetic Sequence       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40<br>41<br>41<br>42<br>43<br>43                                                                                           |

| 7 | <b>Eva</b><br>7.1<br>7.2                                           | Conclusion       4         uation       4         Evaluation Hypothesis       4         7.1.1       Theoretical Performance Improvement       4         Evaluation Methodology       4         Verification of Correctness       4         7.3.1       Sum of Arithmetic Sequence       4         7.3.2       Fibonacci Number       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40<br>41<br>41<br>42<br>43<br>43<br>44                                                                                     |

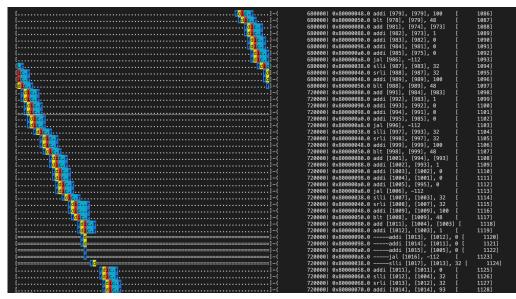

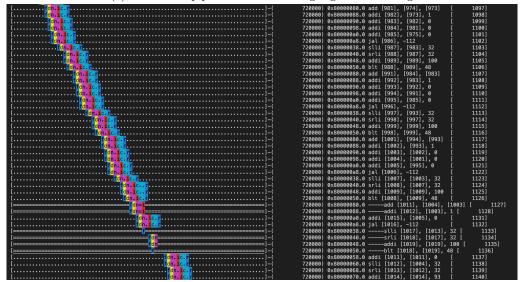

| 7 | <b>Eva</b><br>7.1<br>7.2<br>7.3                                    | Conclusion       4         uation       4         Evaluation Hypothesis       4         7.1.1       Theoretical Performance Improvement       4         Evaluation Methodology       4         Verification of Correctness       4         7.3.1       Sum of Arithmetic Sequence       4         7.3.2       Fibonacci Number       4         7.3.3       Matrix Multiplication       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40<br>41<br>41<br>42<br>43<br>43<br>44<br>46                                                                               |

| 7 | <b>Eva</b><br>7.1<br>7.2                                           | Conclusion       4         uation       4         Evaluation Hypothesis       4         7.1.1 Theoretical Performance Improvement       4         Evaluation Methodology       4         Evaluation of Correctness       4         7.3.1 Sum of Arithmetic Sequence       4         7.3.2 Fibonacci Number       4         7.3.3 Matrix Multiplication       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40<br>41<br>41<br>42<br>43<br>43<br>44<br>46<br>47                                                                         |

| 7 | <b>Eva</b><br>7.1<br>7.2<br>7.3                                    | Conclusion       4         uation       4         Evaluation Hypothesis       4         7.1.1 Theoretical Performance Improvement       4         Evaluation Methodology       4         Evaluation of Correctness       4         7.3.1 Sum of Arithmetic Sequence       4         7.3.2 Fibonacci Number       4         7.3.3 Matrix Multiplication       4         7.4.1 Configurations       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40<br>41<br>41<br>42<br>43<br>43<br>43<br>44<br>46<br>47<br>47                                                             |

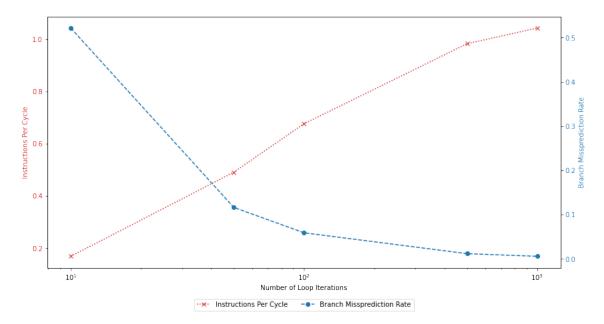

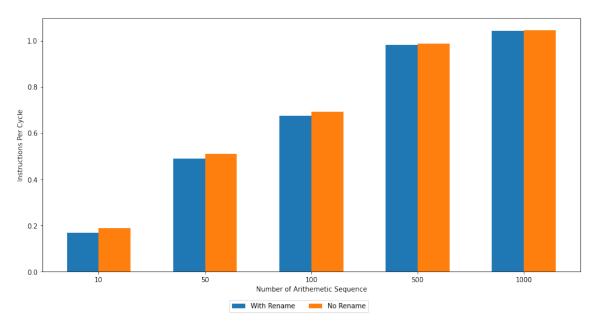

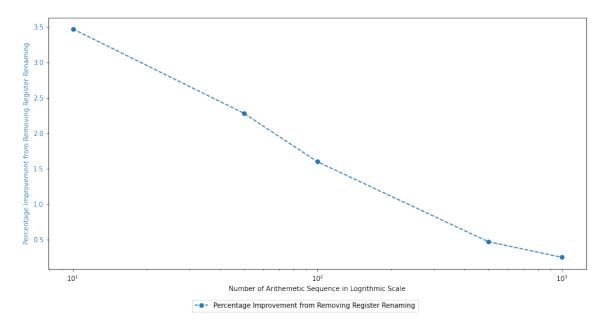

| 7 | <b>Eva</b><br>7.1<br>7.2<br>7.3                                    | Conclusion       4         uation       4         Evaluation Hypothesis       4         7.1.1       Theoretical Performance Improvement       4         Evaluation Methodology       4         Evaluation of Correctness       4         7.3.1       Sum of Arithmetic Sequence       4         7.3.2       Fibonacci Number       4         7.3.3       Matrix Multiplication       4         Performance Evaluation       4         7.4.1       Configurations       4         7.4.2       Result Analysis – Sum of Arithmetic Sequence       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40<br>41<br>41<br>42<br>43<br>43<br>44<br>46<br>47<br>47<br>48                                                             |

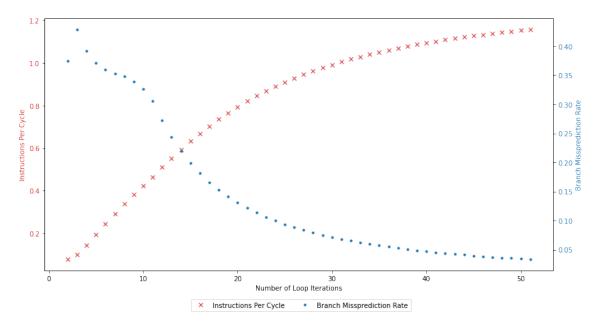

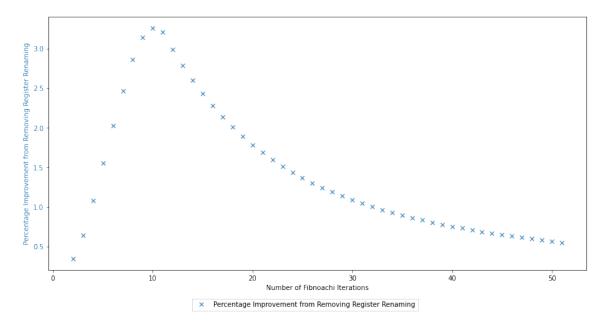

| 7 | <b>Eva</b><br>7.1<br>7.2<br>7.3                                    | Conclusion       4         uation       4         Evaluation Hypothesis       4         7.1.1 Theoretical Performance Improvement       4         Evaluation Methodology       4         Evaluation of Correctness       4         7.3.1 Sum of Arithmetic Sequence       4         7.3.2 Fibonacci Number       4         7.3.3 Matrix Multiplication       4         Performance Evaluation       4         7.4.1 Configurations       4         7.4.2 Result Analysis – Sum of Arithmetic Sequence       4         7.4.3 Result Analysis – Fibonacci Number       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40<br>41<br>41<br>42<br>43<br>43<br>44<br>46<br>47<br>47<br>48<br>51                                                       |

| 7 | <b>Eva</b><br>7.1<br>7.2<br>7.3<br>7.4                             | Conclusion       4         uation       4         Evaluation Hypothesis       4         7.1.1 Theoretical Performance Improvement       4         Evaluation Methodology       4         Evaluation Methodology       4         Verification of Correctness       4         7.3.1 Sum of Arithmetic Sequence       4         7.3.2 Fibonacci Number       4         7.3.3 Matrix Multiplication       4         7.4.1 Configurations       4         7.4.2 Result Analysis – Sum of Arithmetic Sequence       4         7.4.3 Result Analysis – Fibonacci Number       4         7.4.4 Result Analysis – Matrix Multiplication       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40<br><b>41</b><br>41<br>42<br>43<br>43<br>44<br>46<br>47<br>48<br>51<br>53                                                |

| 7 | <b>Eva</b><br>7.1<br>7.2<br>7.3                                    | Conclusion       4         uation       4         Evaluation Hypothesis       4         7.1.1 Theoretical Performance Improvement       4         Evaluation Methodology       4         Evaluation of Correctness       4         7.3.1 Sum of Arithmetic Sequence       4         7.3.2 Fibonacci Number       4         7.3.3 Matrix Multiplication       4         7.4.1 Configurations       4         7.4.2 Result Analysis – Sum of Arithmetic Sequence       4         7.4.3 Result Analysis – Fibonacci Number       4         7.4.4 Result Analysis – Matrix Multiplication       4         Comparison Between Theoretical and Actual Performance Improvement       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 40<br><b>41</b><br>41<br>41<br>42<br>43<br>43<br>44<br>46<br>47<br>48<br>51<br>53<br>54                                    |

| 7 | <b>Eva</b><br>7.1<br>7.2<br>7.3<br>7.4                             | Conclusion       4         uation       4         Evaluation Hypothesis       4         7.1.1 Theoretical Performance Improvement       4         Evaluation Methodology       4         Evaluation of Correctness       4         7.3.1 Sum of Arithmetic Sequence       4         7.3.2 Fibonacci Number       4         7.3.3 Matrix Multiplication       4         Performance Evaluation       4         7.4.1 Configurations       4         7.4.2 Result Analysis – Sum of Arithmetic Sequence       4         7.4.3 Result Analysis – Fibonacci Number       4         7.4.4 Result Analysis – Matrix Multiplication       4         7.4.4 Result Analysis – Matrix Multiplication       4         7.4.4 Result Analysis – Matrix Multiplication       4         Comparison Between Theoretical and Actual Performance Improvement       4                                                                                                                                                                                                                                                                                                              | 40<br><b>41</b><br>41<br>42<br>43<br>43<br>44<br>46<br>47<br>48<br>51<br>53                                                |

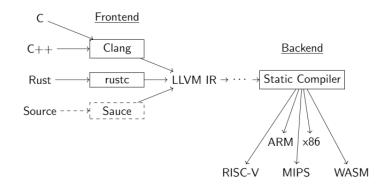

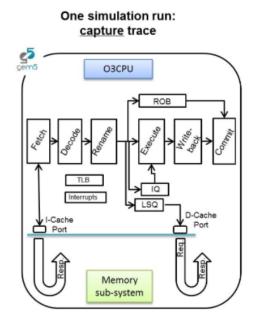

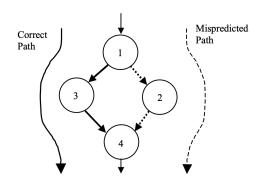

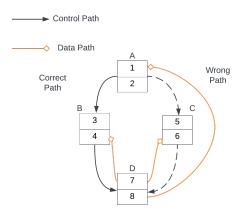

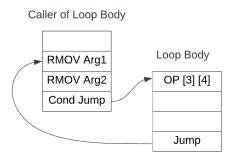

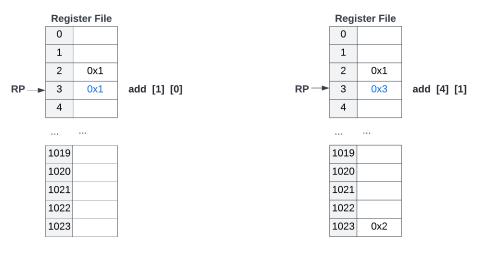

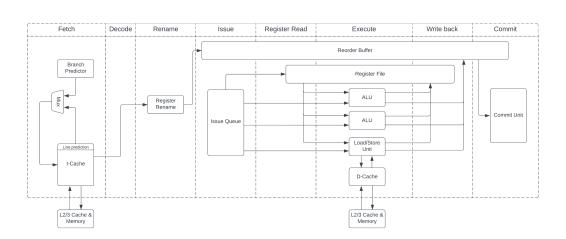

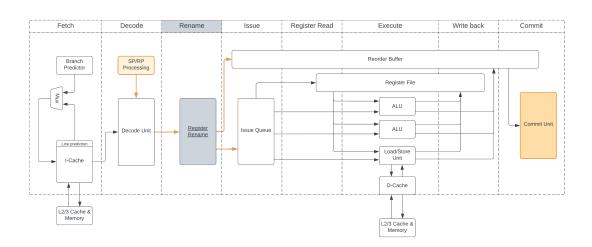

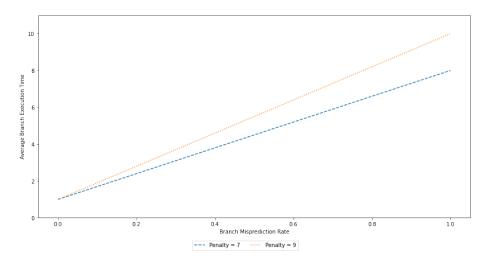

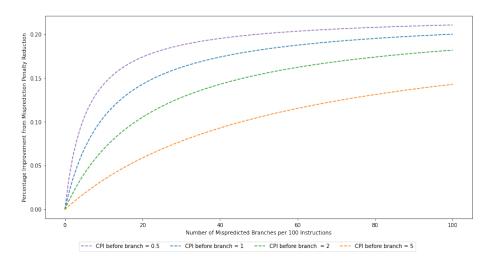

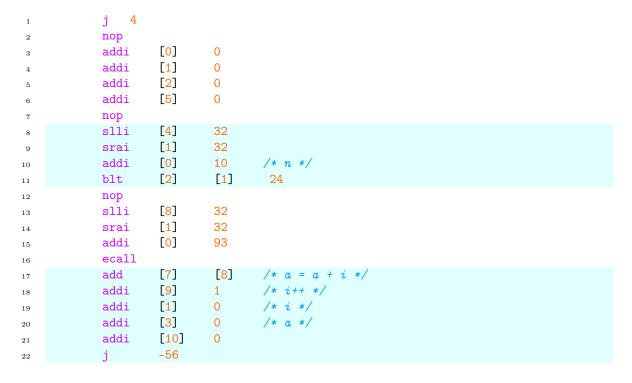

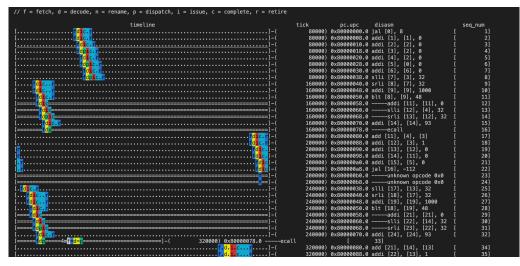

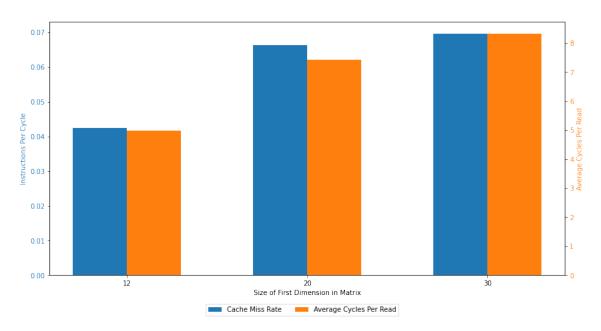

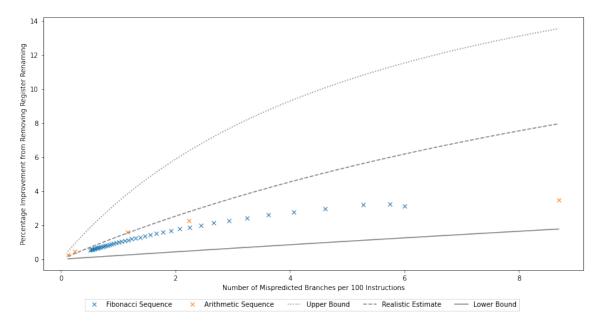

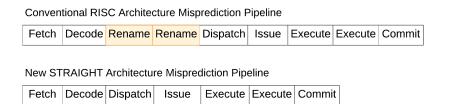

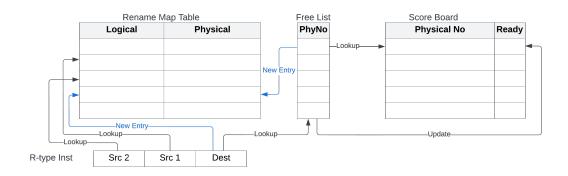

|   | Eva<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6                      | Conclusion       4         uation       4         Evaluation Hypothesis       4         7.1.1 Theoretical Performance Improvement       4         Evaluation Methodology       4         Evaluation of Correctness       4         7.3.1 Sum of Arithmetic Sequence       4         7.3.2 Fibonacci Number       4         7.3.3 Matrix Multiplication       4         7.4.1 Configurations       4         7.4.2 Result Analysis – Sum of Arithmetic Sequence       4         7.4.3 Result Analysis – Fibonacci Number       4         7.4.4 Result Analysis – Matrix Multiplication       4         Comparison Between Theoretical and Actual Performance Improvement       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 40<br>41<br>41<br>42<br>43<br>43<br>44<br>46<br>47<br>47<br>48<br>51<br>53<br>54<br>54                                     |