Imperial College London

IMPERIAL COLLEGE LONDON

DEPARTMENT OF COMPUTING

# Semi-static Conditions in Low-latency C++ for High Frequency Trading: Better than Branch Prediction Hints

*Author:* Maximilian Lucuta *Supervisor:* Dr Paul A. Bilokon

Submitted in partial fulfillment of the requirements for the MSc degree in Computing Science of Imperial College London

September 2023

#### Abstract

Conditional branches pose a challenge for code optimisation, particularly in low latency settings. For better performance, processors leverage dedicated hardware to predict the outcome of a branch and execute the following instructions speculatively, a powerful optimisation. Modern branch predictors employ sophisticated algorithms and heuristics that utilise historical data and patterns to make predictions, and often, are extremely effective at doing so. Consequently, programmers may inadvertently underestimate the cost of misprediction when benchmarking code with synthetic data that is either too short or too predictable. While eliminating branches may not always be feasible, C++20 introduced the [[likely]] and [[unlikely]] attributes that enable the compiler to perform spot optimisations on assembly code associated with likely execution paths. Can we do better than this?

This report presents the development of a novel language construct, referred to as a semi-static condition, which enables programmers to dynamically modify the direction of a branch at run-time by altering the assembly code within the underlying executable. Subsequently, the report explores scenarios where the use of semi-static conditions outperforms traditional conditional branching, highlighting their potential applications in real-time machine learning and high-frequency trading. Throughout the development process, key considerations of performance, portability, syntax, and security were taken into account. The resulting construct is open source and can be accessed at https://github.com/maxlucuta/semi-static-conditions.

# Acknowledgments

Thank you to Erez Shermer, Founder, CTO & MM at qSpark for proposing and formulating the project. A special appreciation is extended to Dr. Paul Bilokon and the qSpark engineering team for their valuable guidance and consistent feedback during the course of the project.

# Contents

| 1 | Introduction1.1Aims and Approach1.2Research Context1.3Report Outline1.4Summary of Achievements                                 | 1<br>1<br>2<br>3                                                       |

|---|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 2 | Background2.1Pipelining and Conditional Branches2.2Dynamic Branch Prediction2.3C++ and Compiler Hints2.4High Frequency Trading | 4<br>7<br>10<br>13                                                     |

| 3 | Research and Development3.1Outline                                                                                             | <b>15</b><br>15<br>15<br>17<br>26<br>30                                |

| 4 | Benchmarks and Applications4.1Outline                                                                                          | <ul> <li>33</li> <li>33</li> <li>36</li> <li>45</li> <li>55</li> </ul> |

| 5 | Evaluation         5.1       Overall Approach                                                                                  | <b>57</b><br>59<br>62<br>63<br>65                                      |

| 6 | Ethics                                                                                                                         | 67                                                                     |

| 7 | Conclusions                                                                                                                    | 68                                                                     |

# Chapter 1

# Introduction

## 1.1 Aims and Approach

The implementation of semi-static conditions, a language construct that can programmatically alter the direction of a branch at execution time, and the identification of instances where it outperforms conditional branching constitute the primary objectives of this project. To achieve this goal, there should be no runtime checks associated with branch-taking. A key challenge in the development process is to create a language construct that mimics the behavior of direct method invocations while simultaneously providing the ability for dynamic switching of branch directions, to facilitate the desired behaviour.

The research contribution of this paper is structured into two stages. In the first stage, the focus is on the development of the construct, with an emphasis on the strategies employed to facilitate low-latency branch-taking through binary editing, addressing the associated considerations of syntax, performance, and portability. The second stage shifts the focus to exploring instances where semi-static conditions out-perform conditional statements, whilst also investigating the implications of runtime assembly modification on hardware behaviour. Additionally, a comprehensive software archive showcasing examples of usage will be created and made readily accessible.

## 1.2 Research Context

Current research in branch prediction optimization is predominantly concentrated on hardware-based solutions that aim to enhance speculative efficiencies and overall performance of modern CPU's. However, despite these efforts, the problem of branch prediction remains unresolved, with limited attention given to softwarebased optimizations [1]. For typical commercial applications, the pursuit of such micro-optimizations is often unnecessary and may introduce additional complexity. Nonetheless, in industries like High Frequency Trading (HFT), even slight improvements in execution latencies on the clock cycle level are highly valued. Consequently, these optimizations are highly sought-after and can provide significant competitive advantages. Due to their crucial role in determining a firm's profitability and success, cutting-edge research on software-based optimizations in such industries is typically shrouded in secrecy.

Several books have attempted to bridge the divide between computational and financial research, aiming to combine mathematical modeling and the development of algorithmic trading strategies (e.g., [2, 3]). Additionally, numerous public conferences are available, focusing on the development of low-latency execution systems (e.g., [4, 5, 6, 7]), emphasizing topics such as data structures, atomics, and low-latency design patterns. Notably, there has been some emphasis on branchless design, which showcases some common alternatives to conditional statements with high misprediction rates [8]. However, the strategies employed in this context lack flexibility and rely on the assumption that branches can be pre-computed without incurring significant costs.

In contrast, there is a wealth of literature and extensively documented resources available for C++ [9, 10], which is widely used as the primary language in the development of low-latency trading systems. However, when it comes to the development of semi-static conditions and strategies involving the modification of running executables using C++, the scope becomes more specialized. Nevertheless, these techniques are well-documented and find applications in various areas such as debuggers, profilers, hot patching software, and security tools (e.g., [11, 12, 13]).

There is a significant scarcity of ultra-low latency C++ tools, particularly those specifically designed to address control flow problems, offering both rigorous application verification and superior performance. While it is possible to come across online posts outlining small-scale experiments that focus on minor branch optimizations in specific scenarios (as demonstrated in [8]), such micro-optimizations are often overlooked and left to the compiler and hardware to handle. Interestingly, extensive research has been conducted on the true cost of branch misprediction [14, 15], highlighting its significant contribution to performance bottlenecks in low-latency systems. While these articles provide in-depth analysis of benchmark data and performance penalties, the strategies proposed for preventing branch mispredictions remain lackluster or non-existent.

In light of existing literature and its insights into software-based branch optimization problems, it becomes apparent that a research gap exists, which this study aims to fill. The motivation behind this research lies in providing solutions to the aforementioned void and contributing to the understanding of software-based branch optimization.

## **1.3 Report Outline**

In Chapter 2, the literature review section of this report, the focus is on encapsulating and critically analyzing research pertaining to the problem at hand. The section begins with an outline of modern CPU pipelined architectures and the implications (and cost) of branched execution. Next, attention is shifted to advancements in hardware-based solutions, outlining the strengths and weaknesses of various schemes when encountering branches of different predictability. The focus is then redirected to software, providing an outline of C++ and its importance in the development of low-latency trading systems. Language features that exist exclusively to optimize branch prediction are also discussed. Finally, discussions are concluded with HFT, examining economic effects, known technical advancements and the problems that remain to be solved in the industry.

Chapters 3 and 4 are dedicated to the research contribution of this report, which can be conceptualized as consisting of two stages: the development of semi-static conditions and data-backed applications. In the development stage (Chapter 3), a sequential approach is adopted to identify the requirements and challenges associated with designing the language construct. The solution to the problem is outlined and demonstrated, providing an overview of key theory with subsequent design decisions and optimizations. The proceeding stage (Chapter 4) demonstrates the instances where semi-static conditions offer superior performance compared to conditional branching, accompanied by detailed analyses and supporting benchmark data to substantiate the findings, alongside novel investigations into effects of binary editing on modern hardware. Furthermore, discussions are conducted on how the outlined scenarios can be incorporated into a commercial trading system, considering their suitability and practical implications.

In Chapter 5, the software contribution alongside the various experimental methods employed to benchmark semi-static checks are critically evaluated. Detailed examples of usage are provided, along with recommendations for maximizing the security and reliability of the language construct. Chapter 6 provides a brief discussion of the ethical implications of this research, with concluding remarks in Chapter 7, discussing potential areas for further research and development.

## **1.4 Summary of Achievements**

The project has achieved significant milestones across multiple dimensions. The research contribution offers valuable insights and approaches for developing softwarebased branch optimizations, with comprehensive and rigorous investigations into the resulting hardware level behaviours, filling an important research gap in the academe. By employing an unconventional yet effective binary editing strategy, the project enables ultra-low latency branch execution through the decoupling of condition evaluation logic and branch taking, controlled directly by the programmer. Through extensive benchmarking and detailed performance analysis in pseudo realistic scenarios, the proof-of-concept semi-static checks demonstrate their real-world applicability, particularly within real-time systems and high-frequency trading.

The research contribution is encapsulated within a open-source library that allows programmers to utilize the language construct for both commercial and experimental purposes. With a focus on syntax, security, efficiency, and portability, semi-static conditions can be seamlessly integrated into high-performance real-time systems, as exemplified in domains such as high-frequency trading and real-time machine learning. This report has since gained significant traction in the high-performance computing space, being featured on the premier newsletter for performance tuning, Easyperf, and considered for publishing by the prestigious Journal of Parallel and Distributed Computing [16].

# Chapter 2

# Background

### 2.1 **Pipelining and Conditional Branches**

The microprocessor is an integrated circuit responsible for executing arithmetic, logic, control, and I/O operations in a digital system [17]. The early 1970's saw the emergence of the first commercially available microprocessor, the Intel 4004, initially designed as a 4-bit 740 kHz central processing unit (CPU) for early printing calculators [18, 19]. Over the past three decades, advancements in integrated circuit technology driven by the exponential growth in transistor density have enabled microprocessor manufacturers to develop increasingly sophisticated CPU's. [20]. Alongside these developments, the introduction of modern instruction sets and standardized operating systems have propelled the computational capabilities of contemporary computers to unprecedented heights.

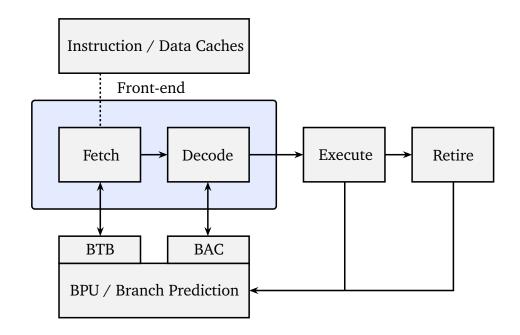

Modern CPU's utilize pipelining as an implementation technique to exploit the inherent parallelism in instruction execution to improve overall throughput [17]. Similar to cars on an assembly line, pipelining allows for the overlapping execution of multiple instructions, with each step in the assembly line constituting a pipe stage that represents a phase in the fetch-decode-execute cycle. If all stages take the same amount of time, a pipeline with *n* stages will achieve a throughput *n* times greater than an un-pipelined counterpart, with the bottleneck stage bounding the number of processor cycles required for a single execution [17]. Whilst Figure 2.1 provides a simplified schematic of instruction pipelining, it is important to note that modern processors have vastly more complex pipelined architectures, often super-scalar with varying instruction sets and addressing modes to prevent memory-access conflicts in instruction/data memory, optimize register handling, and maximize instruction level-parallelism [21].

Pipelining in CPU's, while a powerful optimization technique, introduces hazards that can impact overall performance. These hazards can be broadly categorized into three types: structural hazards, data hazards, and control hazards [17]. (1) Structural hazards occur when hardware resources are incompatible with the sequence of instructions leading to conflicts in resource allocation, resulting in pipeline stalls. However, advancements in super-scalar technology and out-of-order instruction execution have made structural hazards less prevalent to virtually non-existent [17].

|                     |    | Clock number |    |     |     |     |     |     |    |

|---------------------|----|--------------|----|-----|-----|-----|-----|-----|----|

| Instruction number  | 1  | 2            | 3  | 4   | 5   | 6   | 7   | 8   | 9  |

| Instruction $i + 1$ | IF | ID           | EX | MEM | WB  |     |     |     |    |

| Instruction $i + 2$ |    | IF           | ID | EX  | MEM | WB  |     |     |    |

| Instruction $i + 3$ |    |              | IF | ID  | EX  | MEM | WB  |     |    |

| Instruction $i + 4$ |    |              |    | IF  | ID  | EX  | MEM | WB  |    |

| Instruction $i + 5$ |    |              |    |     | IF  | ID  | EX  | MEM | WB |

**Figure 2.1:** Simplified representation of 5 stage pipeline using a RISC instruction set. On each clock cycle, a new instruction is fetched and all proceeding instructions progress to a new pipe-stage in the fetch-decode-execute cycle, achieving a throughput fives times greater than a non-pipelined counterpart. Instruction fetch (IF), instruction decode (ID), execution (EX), memory access (MEM) and write back (WB). Table has been taken and adapted from [17].

(2) Data hazards arise due to dependencies between instructions that have not finished executing, for example, relying on register data that preceding instructions manipulate. These dependencies can cause conflicts and hinder parallel execution, but are broadly mitigated through the use of virtual registers (register renaming) [21]. (3) Control hazards are caused by branch instructions that change the program counter. These instructions introduce uncertainty into the execution flow since the branch target needs to be determined prior to the next instruction fetch [17]. Branches constitute around 12-30% of all instructions executed on modern instruction sets and are widely regarded as the most significant barrier to achieving single cycle executions [22], and as a consequence, have become a large area of focus for optimisations by hardware and software engineers.

Microprocessors employ various strategies to mitigate control hazards in the CPU instruction pipeline. The simplest and most costly approach is a full pipeline stall/freeze, where proceeding instructions after a change in PC are ignored until the target of the branch is known, resulting in a fixed cycle penalty [17, 23]. Improving upon this, processors can make static predictions about the branch target instead of discarding subsequent instructions, maintaining sequential execution of instructions pertaining to either the taken or not-taken branches. By leveraging compiler static analysis and optimizing likely paths of execution, static prediction becomes a powerful optimization technique in pipelined processors, providing non-zero probabilities of correctly predicted branch targets and thus minimising throughput loss from flushes [22, 24]. Though an improvement, this approach is rather inflexible particularly for branch targets that change. Static prediction schemes lack the ability to adapt at runtime to changing patterns in branch target execution which is a common theme for the majority of conditional branches. With modern CPU's employing increasingly more speculative architectures and deeper pipelines to maximise instruction throughput [17], branch penalties become more significant and scale monotonically with pipeline depth [25]. With this in account, it is clear that pro-

| Untaken branch instruction | IF | ID | EX   | MEM  | WB   |      |     |    |

|----------------------------|----|----|------|------|------|------|-----|----|

| Instruction $i + 1$        |    | IF | ID   | EX   | MEM  | WB   |     |    |

| Instruction $i + 2$        |    |    | IF   | ID   | EX   | MEM  | WB  |    |

| Instruction $i + 3$        |    |    |      | IF   | ID   | EX   | MEM | WB |

|                            |    |    |      |      |      |      |     |    |

| Taken branch instruction   | IF | ID | EX   | MEM  | WB   |      |     |    |

| Instruction $i + 1$        |    | IF | idle | idle | idle | idle |     |    |

| Branch target              |    |    | IF   | ID   | EX   | MEM  | WB  |    |

| Branch target + 1          |    |    |      | IF   | ID   | EX   | MEM | WB |

**Figure 2.2:** Example of a five stage RISC pipeline when a branch instruction is correctly predicted to be *not-taken* (top), resulting in subsequent instructions to fall through without hindering overall throughput. Branch target mispredictions (bottom) cause the pipeline to be flushed resulting in idle cycles. Table has been taken and adapted from [17].

cessors require even more aggressive optimisation techniques beyond simple static analysis to minimise idle cycles from branch mispredictions.

The final mitigation technique utilised commonly on classical 5-stage MIPS architectures, but are typically non-existent on modern processors, are branch delay slots which interleave instructions independent to the branch prior to branch target deduction at decode or execute time [26]. The concept is rooted in the observation that not all instructions in a program depend on the outcome of a branch instruction, thereby in theory, allowing the compiler to schedule instructions before the branch is taken and hide some of the branches latency. However, on modern processors, branch delay slots are generally avoided. Utilizing branch delay slots effectively requires the compiler to identify and schedule instructions that can fill the slots, adding complexity to the compiler design and optimization process. Compiler writers need to analyze dependencies, identify independent instructions, and rearrange code to take advantage of the delay slots. This additional burden makes it more challenging to generate efficient assembly and can increase compilation time [22, 26]. With deeply intricate instruction pipelines on modern processors, the scheduling task becomes exponentially more complex and interferes with modern hardware solutions, deeming the once performance-enhancing technique as a complication in modern processors.

Whilst this section offers a fundamental overview of conditional branches and their implications at the processor level, it is crucial to recognize the significance of primitive branch penalty mitigation techniques. These early forms of mitigation laid the groundwork for modern solutions discussed in subsequent sections, with the evolution of speculative processors playing a pivotal role in driving the development of powerful hardware-based branch predictors.

## 2.2 Dynamic Branch Prediction

The advancements of super-scalar technology have introduced increasingly speculative architectures with deep instruction pipelines, effectively maximising throughput to meet the performance requirements of contemporary computers. Consequently, the issue of branch mispredictions have remained a significant impediment to sequential instruction execution [17, 25]. As briefly mentioned earlier, static branch prediction techniques rely on predetermined rules or assumptions rather than leveraging runtime information. To enhance static prediction on modern architectures, compilers play a vital role in making profile-guided decisions based on historical execution patterns. Notably, the binomial distribution of simple branches renders static prediction an effective strategy [17, 27]. Supporting this notion, Fisher and Freudenberger's work demonstrates that applications with statically predictable branches exhibit commendable performance under the current paradigm [28]. The overarching limitation of the former schemes is the inability to adapt to runtime changes, varying input conditions, or capture complex patterns in branch behavior. Whilst previous execution patterns can be used as a proxy to determine the likelihood of a branch, in a real time system with non-deterministic behaviour, solely relying on such a scheme would likely lead to higher mispredictions rates and performance degradation. In light of these issues, a plethora of dynamic branch predictors where developed with the ability to adapt, leverage runtime information, and capture complex branch patterns to improve prediction accuracy and overall performance.

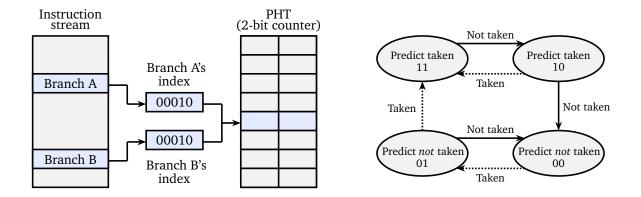

Dynamic branch predictors (BP) can be broadly categorized into one-level local BP's and two-level global BP's, with more modern BP schemes incorporating the strengths of both. One-level BP's typically utilize a one-dimensional branch prediction buffer or branch history table, acting as a cache indexed by the lower bits of the program counter associated with a branch instruction [17, 29]. 1-bit prediction schemes have a single bit entry in the branch history table, indicating whether the branch has recently been taken or not. In the event of a misprediction, the prediction bit is inverted. While this scheme offers simplicity and low hardware overhead, the limited historical information stored in a single bit often leads to frequent mispredictions [17]. To address this limitation, N-bit saturated counter schemes are statically assigned to branches with distinct addresses. When a branch is about to be taken, the counter value associated with the branch is used to select the branch target based on a predetermined threshold [27]. The count is incremented if the branch is taken, and vice versa. It may seem intuitive that increasing the number of bits would improve prediction accuracy through capturing more historical information, however Smith demonstrated that counter sizes larger than 2-bit schemes do not consistently result in higher prediction accuracies [30]. For loop insensitive programs with biased branches, 2-bit counter schemes have been found to be effective with branch misprediction rates averaging at 11%, but performance was found to deteriorate with integer based programs with more complex branch dependencies [17]. The limitations of one-level BP schemes are multifaceted. Relying on a single branch history table restricts the ability to capture intricate patterns and dependencies between branches, hampering the prediction accuracy of one-level BP's [30]. Additionally, interference can occur with branch buffer accesses, as finite space ne-

**Figure 2.3:** Diagrammatic representation of a one-level branch history table with aliasing interference between two branches, taken and adapted from [29] (left). State machine for 2-bit branch prediction, taken and adapted from [17] (right).

cessitates the use of hashing schemes to access the bit-counters for predictions. This can lead to collisions, with negative aliasing occurring more prominently than positive aliasing [29].

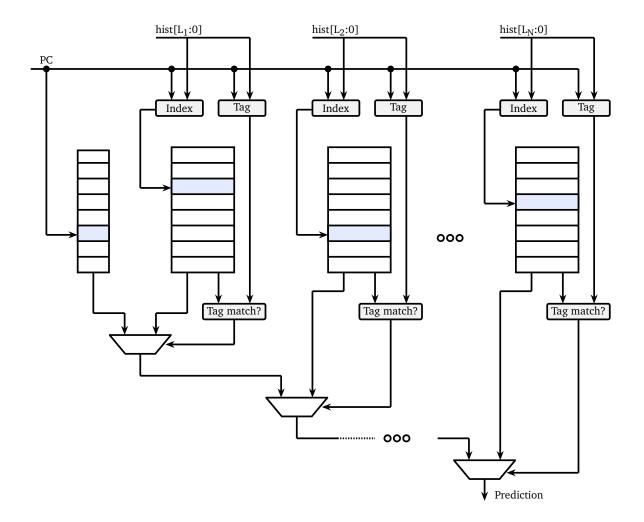

In light of these limitations Yeh and Patt proposed the first two-level adaptive branch prediction scheme, utilising a global branch history table that maintains a shared history of branch outcomes, allowing it to capture patterns and dependencies between branches [31]. Implementation wise, two level BP's comprise of a branch history register (BHR) which tracks recent outcomes of branches and a global pattern history table (PHT) which stores patterns and outcomes associated with specific branch instructions. In this scheme both the BHR and PHT work in collaborative fashion: most recent branch results are shifted into the BHR with branch addresses being used to index a BHR table, the content of the BHR is used to index the global PHT for making predictions, with mispredictions updating both the PHT and BHR [29, 31, 32]. Whilst the two-level adaptive predictor improves prediction accuracy and captures branch dependencies, it still faces challenges related to aliasing conflicts similar to saturated counter-based branch predictors. Yeh and Patt explored several alternative branch prediction schemes based on the original two-level approach, and whilst branch correlation algorithms could be improved it was found that inherent trade-offs existed between efficient storage capacity, memory access overhead and reduced interference, often bounded by physical constraints [32]. As a consequence, current state-of-the-art BP research is focused primarily on the development and optimisation of the prediction algorithms that build off the foundational work originally done by [31, 32], and have been immensely successful at doing so with the emergence of incredibly powerful BP's such as the competition winning TAGE-L with 3-4 mispredictions per 1000 instructions [33, 34].

Whilst the current state of modern BP's are capable of predicting the majority of branches to near perfect accuracy, there exists classes of branches that are inherently hard to predict (HTP) even by TAGE-like predictors, and hence the problem of branch prediction is still considered unsolved [1, 37]. The key weakness arise from attempting to identify correlations between branches in a noisy global history, or

**Figure 2.4:** Organisation of the TAGE (Tagged Geometric) BP with *n*-tagged tables. TAGE features a base 2-bit binomial predictor that provides a basic prediction, and a number of partially tagged tables that store branch history information. At prediction time, each of the tagged tables are indexed simultaneously using global and local branch histories, with the longest tag match generally being chosen to make a prediction [35]. The TAGE-L predictor builds on this and uses a dynamic table organization with varying numbers of tables and table lengths to better capture branch outcomes and histories [36]. TAGE-SC-L further builds on this and incorporates a statistical correlator to further refine predictions [33]. Figure taken and adapted from [35].

the branches themselves are uncorrelated and must rely solely on saturated counter schemes to make predictions [34]. Fundamentally, noise caused by HTP branches introduce a number of redundant patterns which pollute the global branch history causing TAGE-like predictors to struggle, and with non-deterministic orderings of historical patterns, more exotic perceptron based BP's which rely on the position of a branch in the global history also struggle [29, 34, 38]. Problematically, HTP branches are common in most applications but have the more prevalent effects in performance-critical fields such as games, streaming services, and HFT.

The weaknesses of modern BP's stem from their need to be simple, computation-

ally cheap and adaptive to execution phase behaviour [34]. The worst case storage requirements for capturing branch patterns is  $\mathcal{O}(2^n)$ , posing a physical constraint on the predictive capabilities of modern BP's. Whilst fundamental breakthroughs that build off TAGE and perceptron-based BP's have become rare, Zangeneh et al. proposed a convolutional neural network (CNN) BP which can be trained offline [34]. Their work explored two CNN models, one of which was a pure software solution and the second being a smaller hardware optimised version capable of being implemented on chip, both of which showed vast reductions in MPKI on benchmarks run on TAGE-SC-L [34]. Although prediction accuracy greatly improved for correlated branches with noisy histories, BranchNet showed poor performance on datadependant branches and programs where mispredictions are spread across a number of static branches. The reason for the former is that data dependant branches rely on input data and program phase behaviour, meaning there is little to no branch history that can be correlated to data stored in memory, a problem for capturing training data to make predictions [34]. In terms of mispredictions for static branches, this is a problem regarding the sparse storage requirements for a practical CNN BP, though it may be possible to implement larger models using proposed predictor virtualisation techniques [39].

CNN based BP's have the potential to be the next standard for hardware-based BP's, however there is still much work to be done before commercialisation. Whilst the work done by Zangeneh et al. demonstrated MPKI reductions on several HTP branches across a number of benchmarks, the first challenge of using such CNN's would be to achieve generalisation for commercial purposes. This would require a substantially large model (or number of models), introducing additional administrative overhead to the OS [34]. In addition, modern OS's would need to be adapted to load these CNN models on-chip prior to execution time and handle context switching (and its associated penalties) accordingly, in turn adding more complexity and overhead.

At its current state research pertaining to novel hardware based BP's have slowed substantially, and it is likely that modern BP's have reached an asymptotic state of prediction accuracy versus complexity and implementation overhead. Whilst there may be BP's in the future that can have low misprediction rates on noisy or inherently HTP branches, there will always exist some class of branches, especially in real-time systems, that will always be completely non-deterministic and impossible to predict through conventional methods. Whilst this likely can never be solved by hardware, it may be possible that programmatic approaches exist that are able to tame these impossible-to-predict branches.

# 2.3 C++ and Compiler Hints

High-frequency trading (HFT) demands ultra-low latency and exceptional performance, necessitating the selection of a programming language that offers efficient execution, deterministic behavior, and fine-grained control over hardware resources. C++ has emerged as the primary language for developing critical path (path of order action) components in automated trading systems, primarily due to its design philosophy. One fundamental axiom associated with C++ is the "zero overhead principle" [9, 10], which ensures that developers only pay for what they use, resulting in a predictable and transparent performance model. For example, unlike high-level languages that employ garbage collectors to manage memory, C++ utilizes manual memory management. This approach avoids the unpredictable invocation times and overhead associated with garbage collectors, which is critical in low-latency applications that require deterministic performance. C++ provides developers with granular control over memory through abstractions such as pointers, references, heap allocation operators, and standard library methods. However, the trade-off for low-level memory access is increased complexity and the potential for memory leaks and errors. Whilst uncommon, other languages that target the java virtual machine (JVM), for example Java, have become more popular in the HFT space using optimised garbage collection algorithms and compilation techniques to minimise latency cost [40]. Notably, this has become popular with leading quantitative trading firm and liquidity provider, Jane Street.

C++ features also support the shifting of execution time operations to compile time, resulting in the deferral of computational costs and the reduction of runtime latency when appropriately utilized. This capability proves to be a powerful tool for applications with stringent requirements for low latency. Templates, as a Turingcomplete language feature, play a vital role in enabling this paradigm by providing type-safe parameterized blueprints, which allow the generation of specialized code by the compiler for each type-specific instantiation. Consequently, compiletime polymorphism can be achieved, albeit at the expense of flexibility and maintainability [41, 42]. Moreover, the template system can be further leveraged for performing recursive instantiations and type deductions, thereby facilitating the manipulation of types and values and enabling the execution of complex computations at compile time. It is important to note that this approach, known as "template meta-programming," is extensively employed in low-latency settings such as High-Frequency Trading [5, 43].

In the realm of optimizing branch prediction at the language level, specific extensions provided by compilers have long existed, allowing programmers to provide hints for branch prediction. These hints enable targeted optimizations on anticipated execution paths. In GCC and Clang, this capability is manifested in the form of the \_\_builtin\_expect attributes, which allow programmers to specify conditions and associated probabilities (fixed as either 0 or 1) for condition evaluation at runtime [44, 45]. It is worth noting that these so-called branch prediction hints do not directly affect the hardware-based branch predictors and have been ineffective at doing so since the release of Intel's Pentium M and Core 2 processors [46]. Instead, compiler built-ins optimize branch-taking by rearranging assembly code related to branches to exploit processor static prediction schemes and instruction cache effects for improved performance.

Modern processors enhance execution performance by prefetching instructions sequentially from slower to faster memory storage, such as high-speed caches in close proximity to the CPU. This prefetching is done to avoid high memory access latencies during the fetch stages [47]. When executing a code segment containing

| if (condition) | 10af: | je   | 10bd               |

|----------------|-------|------|--------------------|

| function_1();  | 10b1: | call | $<$ function_1 $>$ |

| else           | ()    |      |                    |

| function_2();  | 10bd: | call | $<$ function_2 $>$ |

**Figure 2.5:** Comparison of C++ code without branch prediction hints (compiled with GCC on x86-64). In this case the forward branch (else) is assumed not taken and the backward branch (if) is assumed taken.

| <pre>if (condition) [[unlikely]]     function_1();</pre> | 10af:<br>10b1: | 5    | 10bd<br><function_2></function_2> |

|----------------------------------------------------------|----------------|------|-----------------------------------|

| else<br>function_2();                                    | ()<br>10bd:    | call | <function_1></function_1>         |

**Figure 2.6:** Comparison of C++ code with branch prediction hints (compiled with GCC on x86-64). Since the backward branch is now deemed as "unlikely", the compiler will reorganise the ASM such that the backward branch is now the forward branch and vice versa, in contrast to Figure 2.5.

conditional statements, blocks of sequential assembly instructions associated with different branches are prefetched into the instruction cache, irrespective of how frequently the branches are executed. However, prefetched code that remains infrequently accessed throughout the program's lifespan can contaminate the instruction cache and result in cache-line fragmentation of hot code segments that are frequently executed. This can introduce jitter and latency costs [48, 49]. To optimize branch prediction, the compiler reorganizes the underlying assembly code such that the conditional jump occurs on the least likely path. This is because modern processors initially assume that forward branches are never taken and, therefore, avoid misprediction by fetching the likely branch to the branch target [46]. It is important to note that such static-prediction schemes are employed when the BPU encounters a branch that has not been previously visited. The dynamic prediction schemes outlined in the previous sections will begin to dictate which blocks are speculatively fetched once a branch pattern history has been established.

C++20 introduced the [[likely]] and [[unlikely]] attributes, which serve as wrappers around the original \_\_builtin\_expect attributes and function in the same manner as depicted in Figure 2.6. Apart from this, there have been no other language features attempting to optimize branch prediction [50]. There is limited formal research investigating the performance impact using different benchmarks. However, some online blogs report performance gains (e.g., [48] reports a 15% increase) primarily on branches specifically designed to be highly predictable for demonstration purposes rather than from a research perspective. The fundamental problem with these attributes is that they rely on the programmer's predictive ability of likely execution paths. While profiling and synthetic benchmark data may offer insights into hot/cold branches, programmers tend to significantly underestimate the cost of misprediction when misusing these attributes (for example, a misprediction is likely followed by a cache miss due to the infrequent execution of the unlikely path) [15]. Furthermore, the capabilities of these attributes are confined to compile time, rendering them inflexible to change during program execution. If a branch is indeed more likely to be taken at runtime, the programmer will reap the benefit of the discussed prediction and prefetching semantics. However, if the likelihood of the branch changes during execution, the programmer would have no control over it and would suffer from increased latency through assembly reordering schematics. Real-time systems, which constantly need to react to live events and data, inherently exhibit such variability. Consequently, static language features like these are inadequate as effective branch misprediction mitigators. This inadequacy forms the focus of the research conducted in this report.

## 2.4 High Frequency Trading

The evolution of computer-based trading dates back several decades, starting with the introduction of fully electronic trading by NASDAQ [2]. With the decrease in regulation and advancements in electronic exchanges and telecommunications infrastructure, high-frequency trading (HFT) has gained significant popularity, accounting for over 50% of trading volume in equity markets [51]. Defining HFT itself poses challenges. Haldane [52] emphasizes the use of sophisticated algorithms as its main characteristic, while MacKenzie [53] and Arnoldi [54] highlight the importance of speed in data processing and execution rather than the underlying strategies employed. This report primarily focuses on optimizations that target proprietary automated trading systems, and hence considers HFT as a form of algorithmic trading who's strategies rely on low order execution latencies to ensure profitability.

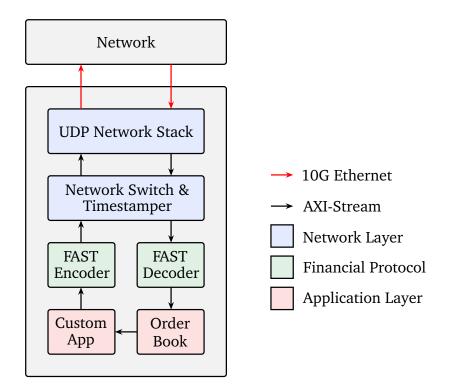

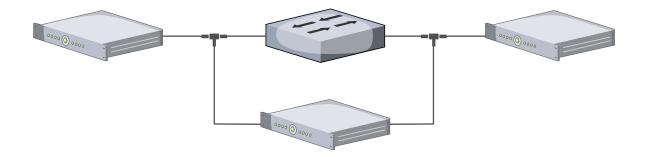

High-Frequency Trading (HFT) firms actively engage in generating trading signals, validating models, and executing trades in order to exploit inefficiencies in market micro-structure within short time frames, with the ultimate goal of achieving profitability [2]. These firms employ diverse strategies to generate profits in financial markets. One prevalent strategy is market-making, where HFT participants continuously provide liquidity by simultaneously placing buy and sell orders, aiming to profit from the bid-ask spread. Another strategy, known as statistical arbitrage, involves capitalizing on transient deviations from fair value by identifying mispricing opportunities. Additionally, event-driven trading strategies focus on leveraging informational asymmetries that arise from significant market events [55]. While a significant body of literature exists on the economic effects of HFT (e.g., [56, 57, 58]), information pertaining to the engineering aspects of low-latency automated trading systems is often concealed due to reasons discussed in Chapter 1. Nevertheless, some online conferences vaguely present important features of HFT systems, such as the networking stack, kernel bypass, custom hardware, and strategies for enhancing the speed and efficiency of production code [4, 5]. An example of a typical HFT system can be seen in Figure 2.7, outlining the relevant components and order flow.

While this report primarily addresses software-based optimizations for latencycritical applications, it is crucial to underscore the significance of the hardware stack

**Figure 2.7:** Simplified anatomy of a HFT system. Exchanges broadcast ticker data along a 10 GiB Ethernet cable to the HFT system, where the networking stack receives and processes packets in user space. Packets are typically compressed in a domain specific format for bandwidth reasons, which are then parsed into meaningful market orders by the financial protocol which are then ordered in the order book. The custom application then issues the buy and sell orders back over the network, this is the area in which the optimisations presented in this report pertain to. Figure taken and adapted from [59].

in HFT firms for trade execution. Simple trading strategies often rely heavily on the networking stack, implemented entirely on custom firmware and Field Programmable Gate Arrays (FPGA) to achieve execution latencies in the nanosecond range [60]. As proprietary software approaches a state of complete optimisation, it is likely that the engineering focus will increasingly shift towards the hardware stack, which is still in its early stages and has considerable room for growth.

# Chapter 3

# **Research and Development**

## 3.1 Outline

This chapter is dedicated to the idea and development of semi-static conditions, outlining theory, design philosophy and optimisations that have been applied iteratively over the development process. The majority of this chapter is focused on developing a prototype that emulates the behaviour of a simple if/else statements, with some discussions given on generalisations to switch statements and non-static member functions in later sections. Whilst discussions on portability are reserved for the evaluation stage, there was an important decision to be made about the choice of development environment for the prototype, more specifically the choice of operating system, compiler and C++ version. Since the primary applications of this language construct will find use in low-latency environments such as HFT systems, the choice of development environment was curated to reflect an industry standard. In light of this, development was done under a Linux OS (Ubuntu distribution) with GCC 13.1 and C++20. At certain stages of the development process, attention will be brought on specific Linux system calls that involve manipulating page permissions for running executables, however equivalent API's exist in other OS's that use paging for virtual memory management.

## 3.2 Semi-static Conditions

Semi-static conditions can be defined as a language construct that emulate the behaviour of conditional statements, but separates condition evaluation logic and branch taking (the subsequent machine code executed on the pretext of the condition). At compile time, the underlying assembly of semi-static branch taking would resemble that of a function call with no indirection, allowing for a deterministic flow of execution with full support of compiler optimisations and hardware intrinsics. In the context of conditional branching, semi-static conditions **remove the runtime check** associated with branched execution, allowing for faster *branch-taking* in low-latency settings. The *semi* part is associated with the polymorphic nature of the language construct: the ability to programatically change the direction of the branch at runtime, whilst maintaining the deterministic compile-time behaviour already men-

tioned. With semi-static conditions, the lines between the compilation and execution phases of a program become blurred, and the nature of the executable shifts from static to somewhat polymorphic or self-modifying. This behaviour manifests itself within the branch-taking mechanism as a single/sequence of assembly instructions that redirect control flow to the respective if or else branches, controlled by branch-switching logic that performs the modification.

In the context of branch optimisation, the philosophy behind the construct is simple. Semi-static conditions remove the runtime check from conditional branches and defers this to an auxiliary method which is directly controlled by the programmer, creating an important decoupling of relatively cheap (branch-taking) and expensive (branch-changing) operations. Isolating branch-switching logic in less performance critical code paths allow conditions (more specifically, those pertaining to hard-to-predict branches) in performance-critical sections to be evaluated preemptively without interference, bypassing the need for branch prediction and eliminating misprediction penalties in the latency-critical path. When the hot-path is executed, no conditional checks are needed and the branch is executed as if it where always perfectly predicted. In instances where code paths are infrequently executed, but contain branches that are often mispredicted, semi-static conditions show promise for optimisations. In addition, the overall cheaper branch-taking that semi-static checks offer show promise for more general use cases, even when branches are well predicted.

In order to realise this language construct, some key challenges are addressed in the development process, which can be broadly split into branch-changing and branch-taking logic. Branch-changing logic needs to be able to find the address of the assembly code instructions to edit in memory, and perform the editing in way that calling the branch-taking method redirects program control flow to user-specified regions based on a runtime condition. Branch-taking logic needs to ensure that control flow is redirected with minimal overhead, so it becomes comparable with the execution latency of a perfectly predicted branch, or a direct function call. At a language level, this is not only dependent upon the underlying assembly instructions that are edited, but also being able to reap the full benefits of compiler optimisations without compromising the safety of the program. On the hardware level, it is paramount that branch-taking code benefits from the same caching, instruction pre-fetching and branch target resolution effects that regular function calls or unconditional jumps do to ensure deterministic and low-execution latencies. Whilst it may be possible to achieve near-identical execution schematics to direct function calls on a language level, the cost of cache incoherence and instruction pipeline stalls can trump branch-misprediction penalties by orders of magnitude, making the construct infeasible in low-latency settings. Therefore, it is crucial that semi-static conditions are compatible in this way with modern hardware and processors. Lastly, and more broadly, the language construct needs to be designed with ease of use in mind. This includes simple and elegant syntax, flexibility and a design that allows it to be easily portable across different architectures, compilers and operating systems.

# 3.3 Prototype Development

The first step in the development process is to establish the desired syntax of the core branch-switching and branch-taking functionality of the language construct. It is likely that this will have a significant influence on the design of semi-static conditions, so establishing how the end product is desired to look in the preliminary stages gives a clear direction in development goals. After careful consideration of simplicity and elegance, the desired usage can be seen below.

```

void function_1() { ... }

void function_2() { ... }

(...)

BranchChanger branch(function_1, function_2);

branch.set_direction(condition);

branch.branch();

```

Semi-static conditions will manifest itself as the BranchChanger class which is instantiated by taking the addresses of two functions as arguments. These functions represent the if and else branches respectively, and their equivalent usage with conditional statements can be seen below.

```

void function_1() { ... }

void function_2() { ... }

(...)

if (condition)

function_1();

else

function_2();

```

The set\_direction method will be responsible for controlling which of the branches is executed based on a user specified runtime condition, whilst the branch method will be responsible for executing the branch with minimal overhead. The signature of the branch method will always be identical to the functions passed as arguments when the class is instantiated, serving as a single entry and exit point for both branches.

Now that a clear high-level design has been established, the next course of action is to implement the branch-taking functionality. Before delving into assembly instruction modification to facilitate the execution of the if and else branches, some thought needs to be given in how the branch method can act as a single entry and exit point for both branches. This method will not do any meaningful work, its sole purpose is to behave as a trampoline to other areas of the code segment while still being able to propagate return values and register data as if one of the branches where called directly. Its first clear responsibility is to set up the call stack in the exact way that the branches would as if they where called in isolation; since control flow will be redirected before the branch function has opportunity to manipulate the stack, in theory the target branches will be able to use any caller-saved data as if it where called directly. To test this theory, we can observe the disassembly for two functions with identical signatures under **-O0** optimisations so any calling behaviour is not omitted.

```

int add(int a, int b) { ... }

int branch(int a, int b) { ... }

(...)

esi, 2

mov

edi, 1

mov

add(int, int)

call

(\ldots)

mov

esi, 2

edi, 1

mov

branch(int, int)

call

```

As expected, both instances follow a standardised calling convention resulting in identical caller behaviour: arguments are pushed from right to left (in this case since there are less than 3 arguments, they are instead moved into registers as per x86 calling conventions) before the subroutine is executed. While this may seem trivial, the standardisation of calling conventions is an extremely important feature of modern compilers that can be leveraged to generalise the branch method in a safe and portable manner.

Now that it's clear that functions with identical signatures observe identical caller setup, and hence the assembly generated on the callee side will be tailored to reflect this, the next course of action is to make the branch entry point mimic the identical signature of the branches passed into the constructor. Using class template deduction, return types and arguments of the branches passed into the constructor can be deduced at compile time and leveraged to generate the correct assembly code for the branch method.

```

template <typename Ret, typename... Args>

class BranchChanger

{

using func = Ret(*)(Args...);

(...)

BranchChanger(func if_branch, func else_branch);

(...)

Ret branch(Args... args);

}

```

The templating splits the signature into arguments and return type, where the arguments are represented by a variadic parameter pack deduced through the pointer types passed into the constructor (represented with the type alias func for readability). These types are then used to declare the signature of the branch method, ensuring that it is identical to the if and else branches. For implementation, virtually anything can be placed inside branch and as long as the return type matches the signature, it will compile. Here there are two main cases to distinguish between; void and non-void return types. If the return type is non-void, returning a brace initialised object of type Ret will suffice for compilation, whereas void return types must be absent of non-void return values. Using std::is\_void\_v<Ret>, we can perform compile time type checking to circumvent this edge case and always ensure compilation for both void and non-void return types.

```

Ret branch(Args... args)

{

if constexpr (!std::is_void_v<Ret>)

{

return Ret{};

}

}

```

Now that the entry point is functional, we can double check the underlying assembly to ensure it has identical caller behavior to the branches. For this example, the branches used to instantiate the construct will be addition and subtraction functions with two integer arguments and an integer return type.

```

lea rax, [rbp-16]

mov edx, 2

mov esi, 1

mov rdi, rax

call BranchChanger<int, int, int>::branch(int, int)

```

From the demangled function call it appears that the correct template is generated, however additional instructions have been added on the caller side. In addition to the integer arguments, an effective address is computed based on an offset from the frame pointer, which is moved into the rdi register after all previous arguments have been set up. From first glance it may be unclear why this is occurring, however when delving deeper into C++ calling conventions, what is happening is an implicit this pointer belonging to the specific BranchChanger instance is being pushed onto the stack [61]. If the branch member function utilised data members specific to the parent instance then this would be necessary, however this not the case and all it does is disrupt register offsets making trampolining to regular functions infeasible. Whilst it may be possible to rectify this programmatically using inline assembly, a safer and more portable solution would be to declare the branch method as static since static member functions are not associated with any particular instance of a class.

```

mov esi, 2

mov edi, 1

call BranchChanger<int, int, int>::branch(int, int)

```

Static declarations allow the branch entry point to work seamlessly, however this limits the number of BranchChanger constructs that can be instantiated per function signature. Template specialisation allows for the differentiation of static branch entry points if the branches passed into the constructor have different signatures, allowing for multiple instances of semi-static conditions in a single program. However if more than one BranchChanger instance exists for a specific signature, this means they will share a common entry point which is problematic: two instances will be performing assembly modification on a single branch method which will have undefined behaviour. A way to circumvent is would be to alter the return types of the branches with other built-in or custom types to ensure that different templates are generated. Given these trade-offs, the priority for development is to work as much as possible with the compiler to avoid writing inline assembly for safety and portability reasons, and hence the final decision was to keep branch declarations as static.

Before moving onto implementing assembly modification, an important caveat to consider is compiler optimisations. From the compilers perspective, the branch method is a small function that does not produce any meaningful work making it susceptible to inlining or dead code elimination [62]. Obviously, if this happens then the construct will be unusable, but limiting its usage to programs that are intended to be run on **-O0** defeats the purpose of it being used in high performance applications. The simplest solution would be to disable optimisations specifically on the branch method, which can be achieved on GCC using pragma directives or more elegantly using attributes.

```

--attribute_- ((optimize("O0")))

static Ret branch(Args... args)

{

if constexpr (!std::is_void_v<Ret>)

{

return Ret{};

}

}

```

**Assembly Editing** Now that the entry point is fully functional, development can start for the core assembly modification functionality. The target for this editing will the prologue instructions of the branch method, specific to each instance produced by template specialisation of the parent BranchChanger class.

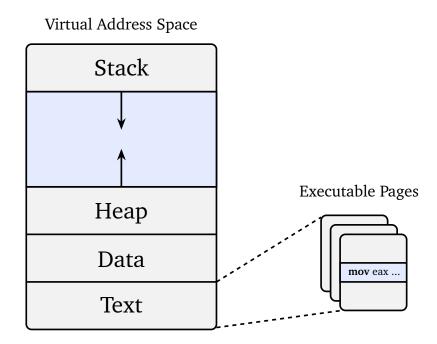

The first course of action is identifying the addresses of the machine code instructions to edit. In terms of the virtual address space, the machine code instructions of interest pertaining to the executable reside in the text segment, which itself is mapped by pages with read-only and execute permissions. Before we can perform any modifications, the page where the function prologue resides must be located

**Figure 3.1:** Simplified representation of virtual address space segments, with lower segments residing at lower memory addresses. Blue segment highlighted in executable page represents an offset where a specific instruction can be found.

and its permissions must be changed to read/write, otherwise the processor will raise a segmentation fault if any memory stores are attempted. Modern operating systems employ address space layout randomisation (ASLR) by randomising the base address of the virtual address space to prevent attackers from exploiting known memory addresses, so locating executable pages must be deferred to runtime [63]. Upon construct instantiation, we can generate a pointer to the template specialised branch method which is essentially the logical address of the first instruction pertaining to the function. To obtain the address of the page boundary in which the function resides, we can compute the page offset through the modulo of the logical address and the page size of the system (which can be obtained using the Linux specific getpagesize method), and then subtracting this offset from the original address to align it with the lowest multiple of the page size. To change the page permissions, we can use the mprotect system call to alter the flags of the VMA (virtual memory area, a kernel data structure which describes a continuous section in the processes memory) corresponding to the page address previously computed [64].

```

uint64_t page_size = getpagesize();

address -= (uint64_t)address % page_size;

mprotect(

address, page_size, PROT_READ | PROT_WRITE | PROT_EXEC

);

```

Now that we have located the instructions in memory to edit (through the pointer to

the branch function), and made this editing permissible through altering the page permissions where the function resides, we can start adding instructions to redirect control flow to the branches. With latency in mind, the scope of control flow instructions that can be used become limited to direct jumps or calls, which conventionally cannot be polymorphic without employing assembly editing. On x86 architectures, jumps and calls redirect control flow by supplying a relative 32-bit offset from the current program counter, which is reduced to a simple signed displacement arithmetic operation.

| 00000000000011a9  | <foo>:</foo>   |         |                  |

|-------------------|----------------|---------|------------------|

| 00000000000011a9: | f3 Of 1e fa    | endbr64 | 4                |

| 0000000000011ad:  | 55             | push    | rbp              |

| 0000000000011ae:  | 48 89 e5       | mov     | rbp,rsp          |

| ()                |                |         |                  |

| 0000000000011e3:  | 55             | push    | rbp              |

| 0000000000011e4:  | 48 89 e5       | mov     | rbp,rsp          |

| 0000000000011e7:  | e8 bd ff ff ff | call    | 11a9 <foo></foo> |

| 0000000000011ec:  | b8 00 00 00 00 | mov     | <b>eax</b> ,0x0  |

Above is an example of the machine code generated for a call instruction (achieved with **objdump -d -M intel**) along with the program counter (left) and equivalent assembly (right). Focusing on the call instruction with opcode **e8**, we can see the following 4-byte displacement encoded as a signed hexadecimal value in little endian format (architecture specific). The signed 2's compliment equivalent of this displacement is -67 bytes, which is 5 bytes smaller than the displacement from the PC of the call instruction (**11e7**) to the function entry point (**11a9**). The reason for this is because the offset of relative jumps are computed from the last byte of the instruction to the first byte of the target address, which can be formally described with the equation:

Jump Offset = Target Address - Entry Point - Size of Instruction

Fundamentally, relative jumps are indeed branches and introduce control hazards in pipelined processors, but have subtly different prediction schemes and penalties on the micro-architectural level in comparison to conditional jumps and indirect jumps (through register data). Prediction schemes for direct jumps occur relatively early in the pipeline (processor front-end), whereas branches that have data dependencies (such as indirect jumps/calls) or are conditional on FLAGS can get deep in the pipeline (back-end) execute stages before mispredictions are discovered, and hence incur a higher penalty when previous instructions need to be flushed. For relative jumps, the first line of prediction occurs in the branch target buffer (BTB) which acts as a specialised cache to predict weather the PC resolves to a branching instruction, and if so, what block to fetch next [17]. This is especially important for speculative prefetching: the instruction prefetcher needs to know in advance which blocks to fetch next, so if the PC is a branch, it can can steer the prefetcher to the predicted

**Figure 3.2:** Simplified representation of the interaction of caches and branch prediction schemes on the instruction pipeline. Unconditional branch mispredictions are resolved at the decode stage by the BAC, whereas conditional branches are resolved at the execute stage. Information of retired predicted and mispredicted branches are fed into the BPU to update the predictor.

branch target and begin bringing the associated instructions into lower level caches. If predicted correctly then virtually no penalties are incurred as for conditional and data dependant branches, however the distinction occurs at the pipeline stage where mispredictions are detected and resolved. When an instruction reaches the decode stage, more information is attained surrounding the nature of the instruction. The branch address calculator (BAC) will ensure that the branches have the correct target by computing the absolute address of the PC and comparing it with the supplied target. If a direct jump is mispredicted at this stage, this means that the supplied branch target does not match the predicted, and proceeding instructions that have been incorrectly fetched will be flushed and the prefetcher will be re-steered to the correct branch target [65]. In regards to conditional branches, the same applies with the BAC however mispredictions are ultimately detected later in the execute stages which result in more severe pipeline stalls. On processors with branch order buffers (BOB), the recovery process can start before the processor pipeline has been flushed, but nevertheless the relative cost for mispredicted unconditional branches is much lower than conditional branches [65].

It is clear that relative jump/calls provide the cheapest means of control flow alteration, providing that the size of the jump does not exceed  $2^{32}$  bytes. The question that remains is which instruction would be most suitable from a latency and implementation perspective. Call's and jumps are very similar mechanically, with calls being a two-part atomic operation which jumps to an offset while pushing the return address onto the stack. From a latency perspective, while minimal, the additional use of the call stack pollutes data caches unnecessarily and the additional return instruction introduces more branching which is prone to mispredictions. However the main challenge comes from a development perspective; after the call is complete (within the branch method), the return address will be the proceeding instruction which may involve manipulating data on the stack/registers which have already been dealt with. Ensuring this does not occur for all possible signatures is tedious, and may limit future optimisations on the language construct. Using a jump will be much simpler; we can simply go straight to the branch without needing to ever complete execution of the entry point, and when the branch has finished executing, control flow will be redirected to the original calling site of the branch method (recall that a ret instruction is a jmp [reg]).

To implement the jump, the first thing we do is alter the opcode of the first instruction pertaining to the branch method to **e9** (jmp opcode on x86) through its pointer, and then increment it. The following 4 bytes will be reserved for the relative offsets from the current program counter. To compute the offsets, we simply use pointer arithmetic to compute the displacement in memory from the branch method to the respective if/else branches, then subtracting the length of the instruction from the offset as specified in the formula mentioned earlier. Next, the the integer offsets are converted into 4-byte hexadecimal representation and stored in a two dimensional member array (total of 8-bytes), accounting for architectural byte ordering.

```

unsigned char offset_in_bytes[DWORD] = {

static_cast < unsigned char > (offset & 0xff),

static_cast < unsigned char > ((offset >> 8) & 0xff),

static_cast < unsigned char > ((offset >> 16) & 0xff),

static_cast < unsigned char > ((offset >> 24) & 0xff)

};

#if __BYTE_ORDER__ == __ORDER_BIG_ENDIAN__

change_byte_ordering(offset_in_bytes);

#endif

```

std::memcpy(dest\_array, offset\_in\_bytes, DWORD);

**Changing Branch Directions** At this point the development of the construct is nearly complete, leaving only the direction changing method for development. With the offsets computed and stored in a class member array, setting the branch direction would simply involve a memcpy of these bytes to the branch pointer as the destination address. Direction setting must be initially done upon instantiation, since altering the first byte of the branch entry point will result in a jump to an undefined location, likely causing a segmentation fault. The class was adapted to have an optional parameter in the constructor to specify the initial direction of the branch, with the default condition being true. This can be conceptualised as a similar scheme to compiler branch prediction hints; the programmer can specify the likely direction which the branch would first be taken, but will still have the control to change

this at any given time. The actual set\_direction method will use boolean indexing (the boolean being the runtime condition passed to the method) to access the bytes pertaining to the correct branch, which are copied into the 4 byte slot next to the jmp opcode. The boolean indexing approach is simple, and allows for active cache warming if desired.

```

void setDirection(bool condition)

{

std::memcpy(dest, src[condition], DWORD);

}

```

**Concluding Remarks** Upon testing, the semi-static conditions prototype appears to work seamlessly for varying branch signatures on all optimisation levels. Whilst it is not possible to observe the assembly editing in real time without specialised disassemblers (for example, **objdump** only shows the contents of the object file which is not edited, rather the pages that are mapped by it), using **perf record** it is possible to observe it indirectly through the percentage cycles spent in the branch method.

```

Percent |

BranchChanger<int, int, int>::branch(int, int)

100.00 | push %rbp

mov %rsp,%rbp

mov %edi,-0x4(%rbp)

mov %esi,-0x8(%rbp)

mov $0x0,%eax

pop %rbp

ret

```

Above shows the disassembly of the branch method with the percentage cycles spent on each instruction on the left hand side, obtained using **perf record**. The branches used in this example are simple addition and subtraction functions. The data shows that the first instruction within branch constitutes all the cycles spent in the function entirely; this is the instruction that is edited to a jump and hence it is expected that this is the only instruction that executes for the duration of the program. The branches themselves have a small percentage of cycles spent relative to all other methods in the test program, which supports that the branches are in fact executed and control flow is redirected accurately, this is also confirmed by simply printing the return values to the standard output. All the above, along with correct program behaviour, suggest that the language construct works as intended. Now the core prototype is complete, thought can be given into optimisations for branch taking and branch changing, as well as additional features that expand from this core concept (switch statements, also class member functions which observe different calling behaviour than conventional functions).

# 3.4 Optimisations

So far, the prototype demonstrates a proof-of-concept, but not a final product. The overarching goal of this language construct is to provide deterministic (low standard deviation) and low latency branch taking in scenarios where misprediction rates are high. Although mispredictions on the processor level are expensive, if the branch-taking component does not perform at a similar level to perfectly predicted branches, the construct will not find use in performance sensitive environments. Prior to running benchmarks, it is crucial that we level the playing field as much as possible to make semi-static conditions competitive.

**Branch Taking Optimisations** Naturally the most obvious place to start is the branchtaking method itself. In the development process, we ensured that the first instruction executed within branch is a jump that detours execution to one of the branches, so the processor does not waste any time executing instructions it does not need to. This is fine, however the glaring bottleneck arises from having to prevent all compiler optimisations on the method, which was implemented as a one-hot fix to prevent the function from being eliminated. Ideally, the entry point should benefit from all optimisations that regular functions do, but have the minimum amount of problematic optimisations disabled. The first obvious approach is do only disable in-lining for the entry point; this is destructive as the compiler will place the body of the function pre-editing within the calling site which essentially does nothing. Even if it managed to inline the edited assembly, it will be completely infeasible to target the in-lined instruction within the code segment. Replacing the compiler attribute on branch with \_\_attribute\_\_((noinline)) generated the following assembly under **-O3** optimisations.

| 00000000000118c:  | lea | rdx,[rip+0x26d]                   |

|-------------------|-----|-----------------------------------|

| 000000000001193:  | lea | rax,[rip+0x136]                   |

| 00000000000119a:  | sub | rax,rdx                           |

| 00000000000119d:  | sub | rax,0x1                           |

| 00000000000011a1: | mov | <b>DWORD PTR</b> [rip+0x25a], eax |

|                   |     |                                   |

Surprisingly, even with the noinline directive the compiler still reduced the branch call to the lea instructions highlighted in bold. Upon further research into the effects of GCC compiler attributes, what appears to be happening is that the inlining prevention does in fact take place, but the compiler deems the function to have no side effects and as a result optimises out the call completely. A simple way to control this optimisation is by inlining assembly within the function body; inline assembly adds uncertainty to the compilers optimiser as it cannot determine if it has side effects on register or memory values. Adding a simple asm("") which does not produce any meaningful work is sufficient to prevent optimising out the function call in addition to using the noinline attribute.

Further testing revealed an interesting yet problematic optimisation, calls to the original branch method where replaced with calls to a different branch method, of

which the compiler duplicated and altered a number of instructions within the body. Below is an example of both instances, with demangled function names simplified for readability.

```

000000000001280: <_BranchChanger_branch.constprop.0.isra.0>

000000000001280:

ret

000000000001281:

cs nop WORD PTR [rax+rax*1+0x0]

000000000001288:

nop

00000000000128b:

DWORD PTR [rax+rax*1+0x0]

nop

(...)

000000000001290: <_BranchChanger_branch>

000000000001290:

endbr64

000000000001294:

xor

eax, eax

000000000001296:

ret

```

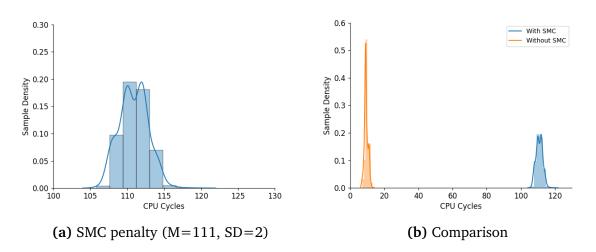

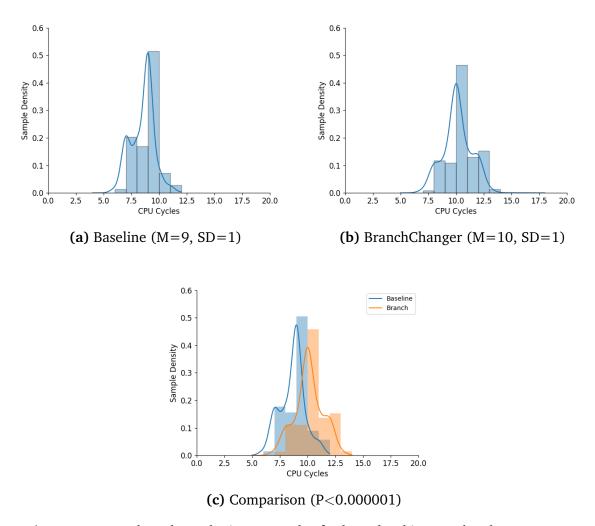

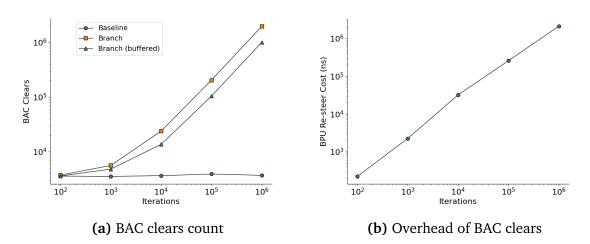

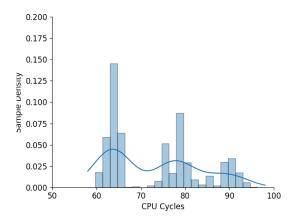

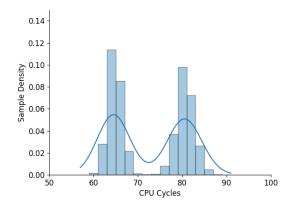

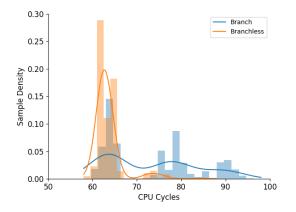

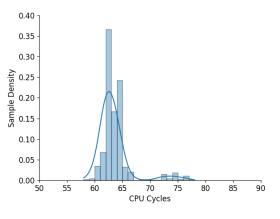

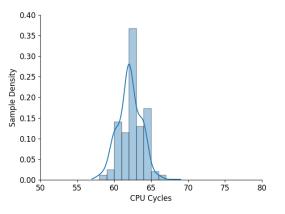

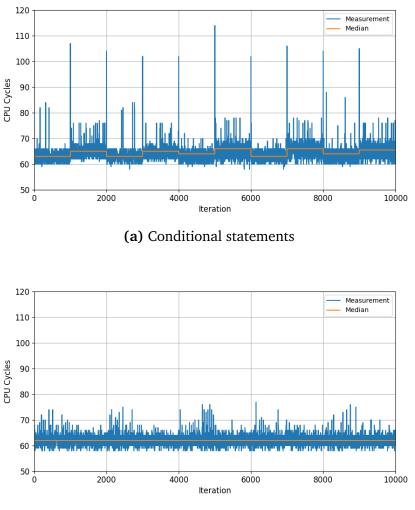

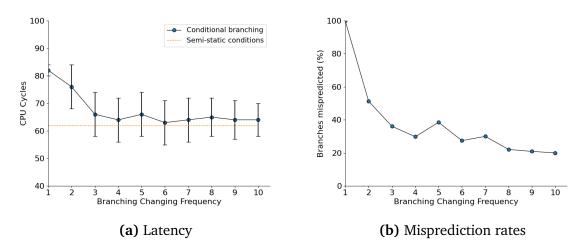

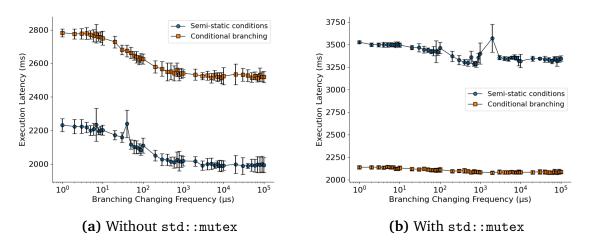

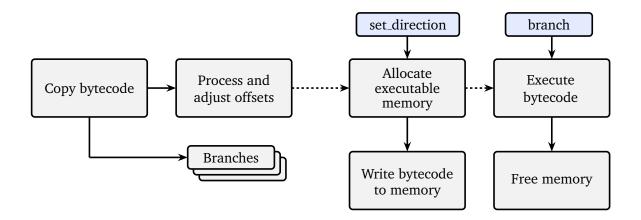

The first example of the branch method represents the duplicated form which is called, whereas the second example represents the method which is needed to be called to allow semi-static conditions to work. Inspecting the demangled name of the duplicated function reveals the optimisation that has been applied: interprocedual constant propagation (ICP) [66]. This optimisation is multifaceted; when the compiler recognises that a function call has some arguments passed as constants, it creates a spot-optimised clone of the function which can involve removing redundant computations and memory accesses. This can be seen in the constprop version; the primary instruction becomes a ret because the compiler can see that the branch method does not produce any meaningful work, the remaining instructions are included as padding to align the function on a 16-byte boundary. This padding is important especially for procedural calls since most modern processors fetch instructions on aligned 16-32 byte boundaries; fetching code after after an unconditional jump costs a few clock cycles however this delay is worsened if the branch target does not lie on a 16-32 byte boundary [61]. Following this, an interesting observation can be made in regards to the original branch method. In many instances, the function itself does not follow alignment and as a result the compiler seems to always place it at the bottom of the text segment to prevent misalignment of all other procedures in the executable. Another interesting observation is that the constprop version is often placed close to hot code paths in the text segment (often very close to main), which can reduce instruction cache fragmentation by placing contiguous subroutines relatively close to one another.